INTRODUCTION

The CM7120 is a highly-integrated Audio DSP and CODEC Hub system. It combines advanced big and little DSP architecture with a high-performance and flexible CODEC hub, making it ideal for a wide range of mobile systems, such as Smartphone, Tablet, and Headset devices.

The CM7120 integrates two DSP cores with extensive memory resources. Given the advanced big and little DSP architecture, Tensilica HiFi-3 DSP core can support complicated signal processing applications with 300MIPS speed. Tensilica HiFi Mini DSP core can support light and ultra-low power applications, such as voice trigger and voice command. Given that Tensilica HiFi-3 and Mini DSP cores are widely used by many third-party software developers, it makes CM7120 create an extensive wide software reference design ecosystem, including multi-microphone advanced voice processing (NS, AEC,…etc.), voice trigger, command and high-quality, well-known branding audio post-processing.

The CM7120 integrates various method of the DSP code loading from SPI, I2S, UART and JTAG interface and supports auto code loading from external flash memory. Its fully-flexible digital mixing and routing with asynchronous sample rate converter (ASRC) supports the DSP core for wide use case flexibility. Five digital audio interfaces are provided, supporting I2S/PCM/TDM audio formats. Four differential analog microphone inputs and up to eight digital microphone inputs can accept audio signals from multiple microphone or line input sources.

The CM7120 features a low power cap-free Class-G headphone amplifier. It consumes low power during playback with 114dB SNR performance, providing mobile system longer battery life under Hi-Fi listening experience. Mono Receiver amplifier provides 100mW/16Ω or 32Ω with 3.3V supply or 3.6V~5V to 3.3V embedded LDO power source and high SNR, THD+N and good PSRR on GSM 217Hz.

The CM7120 also combines a variety of low-power fixed-function signal processing components. The advanced multiband DRC (Dynamic Range Control) enables further digital audio processing capabilities on playback or record paths. Advanced DRC function comprises multi-section and multi-band parts, ensuring signal level maintenance, maximizes loudness, and prevents audio clipping and speaker damage. The 22-band parametric EQ consists of 11-band EQ for each L/R playback path. Each bands of EQ can be programmed independently to compensate frequency response of L/R speakers, and to meet various user preferences. An independent 12-band parametric Equalizer consists of 6-band EQ for each L/R channel on the record path, for compensating the frequency response of microphone/line inputs.

The CM7120 individual blocks are all design for power efficient target, helping devices to achieve long time playback, record, voice talk…etc. cases. The CM7120 is supplied by a small WLCSP package, ideal for mobile system design.

PRODUCT FEATURES

DSP and Digital Features

Tensilica Hi-Fi 3 and Hi-Fi Mini DSP Cores

- Hi-Fi 3, 300MIPS

128KByte IRAM

128KByte DRAM

- Hi-Fi Mini, 50MIPS

40KByte IRAM

80KByte DRAM

- 192KByte SRAM for Hi-Fi 3 and Hi-Fi Mini DSPs sharing

- Watch dog function

- Support DSP wake-up by I2C/SPI command

- Firmware code loading by SPI I/F with CRC function

Auto Load DSP Code from External Flash Memory through SPI

Five 8~32bits / 8kHz ~ 192kHz I2S/PCM/TDM Interfaces

- Two I2S/PCM/TDM interface with ASRC function

- Three I2S/PCM interface with ASRC function

UART Interface

- Support I/Os: RTS# / CTS# / Tx / Rx 4 Pins

- Baud Rate up to 5Mbps

S/PDIF-In support up to 24bit Format and 192KHz Rate

I2C Control Interface

- 1 Slave Mode I2C Control Interface (Up to 2MHz Clock Rate)

- 3 Master Mode I2C Control Interfaces (Up to 2MHz Clock Rate)

SPI Control Interface

- 1 Slave Mode SPI Control Interface for DSP firmware code loading (Up to 30MHz Clock Rate)

- 2 Master Mode SPI Control Interfaces (Up to 2MHz Clock Rate)

Two Independent PDM Interfaces

- For External PDM Amp

- 4 Channels Playback simultaneously

Support 4 stereo digital microphone interfaces for 8-CH recording

- Independent digital microphone clock output (DMIC1/2/3/4_CLK)

- Dynamic DMIC clock on/off function for saving power at VAD mode

Support SPI Flash Controller (Up to 30MHz clock rate)

- Support 24-bits or 32-bits address length

Configurable Multi-band Parametric Equalizer (EQ)

- 11+11 bands for DAC L/R path (2*LPF + 3*HPF + 5*BPF + 1*Biquad)

- 6+6 bands for ADC L/R path (1*LPF + 1*HPF + 4*BPF)

- Mono DAC/ADC EQ mode for power saving

DRC

- Three-bands DRC with crossover filter for playback path

- Dedicated DRC for DAC playback path

- Dedicated DRC for ADC record path

- Complement with Front-end Analog PGA for record path

VAD (Voice Active Detection) with internal 32K memory

- Flexible buffer read point control for reduce key phrase detection latency

- Human Pitch Detection to avoid false alarm

Sidetone Generator

Signal Generator for Vibrator

Power Key Press Detection for avoiding pop noise when system hang up

Analog Features

Stereo Headphone Output without DC Blocking Capacitors

- SNR=114dBA (RL=32 Ohm, HPO=25mW, 20 ~ 20kHz)

- DNR = 108dBA (Input=-60dBFS, RL=32 Ohm, HPO=25mW, 20 ~ 20kHz)

- THD+N = -93dB (RL=32 Ohm, HPO=20mW, 20 ~ 20kHz)

- FSOV=1Vrms (RL=32 Ohm, 20 ~ 20kHz)

- Crosstalk < -100dB (32Ohm, 1kHz)

- PSRR > 80dB (Vripple=100mVrms, 20~5kHz)

Impedance sensing for headphone output

- Independent detection for L-CH and R-CH of headphone device

- Support 10 steps impedance sensing (0 ~ 8ohm / 9~23ohm / 24~41ohm / 42~75ohm / 76~150ohm /

151~450ohm / 451~1000ohm / 1000 ~ 5kohm / 5kohm ~ 50kohm / >50kohm (Floating State) )

- Auto mapping the adaptable gain for HP FSOV by impedance sensing results

Headphone de-pop function

- Offset level <= 100uV

Stereo Single-End or Differential Line Output Port

- SNR = 114dBA (RL=32 Ohm, 20 ~ 20kHz)

- DNR = 101dBA (Input=-60dBFS, RL=32 Ohm, 20 ~ 20kHz)

- THD+N = -97dB (RL=32 Ohm, 20 ~ 20kHz)

- FSOV >= 1Vrms

- Crosstalk < -80dB (Loading>=600 Ohm, 20 ~ 20kHz)

Mono Differential Receiver Amp Output

- Noise level < 8uV (16Ohm, 20 ~ 20kHz)

- 50mW (VDD=3.3V, THD+N < 0.01%, 16Ohm, Differential)

- 5mW (VDD=3.3V, THD+N < 0.01%, 16Ohm, Differential)

- 100mW (VDD=3.3V, THD+N < 0.03%, 16Ohm, Differential)

- 104mW (VDD=3.3V, THD+N < 5%, 32Ohm, Differential)

- 115mW (VDD=3.3V, THD+N < 10%, 16Ohm, Differential)

- PSRR >= 80dB (Vripple = 100mVrms, 20 ~ 5KHz)

Mono Receiver Amp de-pop function

- Offset level <= 100uV

4 Analog Input Ports Support 4 CH Analog MIC Recording

- Differential/Single-End analog microphone inputs with boost pre-amplifiers and low noise

microphone bias

- SNR=100dBA (single-ended/differential mode, 0dB gain, Vref=FSIV, 20 ~ 20kHz)

- THD+N=-94dB (single-ended/differential mode, 0dB gain, Vref=FSIV, 20 ~ 20kHz)

- THD+N=-80dB (single-ended/differential mode, 20dB gain, Vref=FSIV, 20 ~ 20kHz)

- THD+N=-75dB (single-ended/differential mode, 40dB gain, Vref=FSIV, 20 ~ 20kHz)

- Boost gain range: -12dB ~ +39.75dB with 0.75dB/step

Headphone or Handset Detection Function

- One pin to support microphone detection

MICBIAS

- MICBAS1 for Headset MIC, Adjustable Output Voltage (2.3V/2.5V/2.7V)

- MICBAS2 and MICBIAS3 for AMEMS MIC, Adjustable Output Voltage (1.8V/1.9V/2.0V/2.7V)

- High PSRR and Low Noise

Three inside PLLs with Wide Range Clock Input (For Tensilica DSP and Codec)

Multi-Buttons Detection

4 Buttons Detection

- Button1 Resistance Range support 0~70 Ohm (The value is parallel with RMIC)

- Button2 Resistance Range support 110~180 Ohm (The value is parallel with RMIC)

- Button3 Resistance Range support 210~290 Ohm (The value is parallel with RMIC)

- Button4 Resistance Range support 360~680 Ohm (The value is parallel with RMIC)

3 Buttons Detection

- Up Button Resistance Range support 150~280 Ohm (The value is parallel with RMIC)

- Center button Resistance Range support 0~50 Ohm (The value is parallel with RMIC)

- Down Button Resistance Range support 550~650 Ohm (The value is parallel with RMIC)

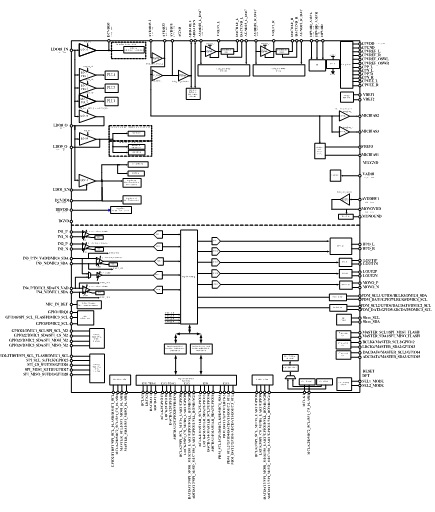

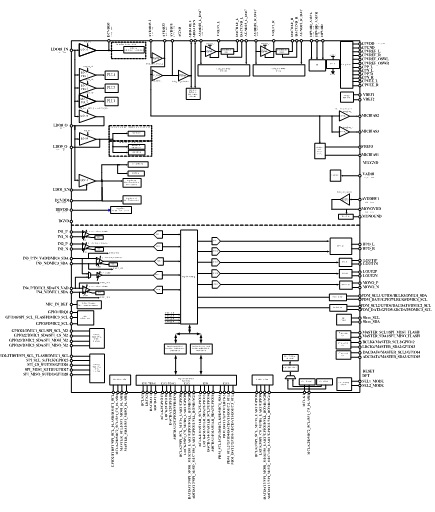

BLOCK DIAGRAM