# Sil9612 4K Video Processor with Integrated 300 MHz Receiver and Transmitter

**Data Sheet**

Sil-DS-1120-C

April 2017

# Contents

| 1. Gene | eral Description                                       | 7  |

|---------|--------------------------------------------------------|----|

| 1.1.    | Video Processor                                        | 7  |

| 1.2.    | On-screen Display                                      | 7  |

| 1.3.    | Video Input                                            | 7  |

| 1.4.    | Video Output                                           | 7  |

| 1.5.    | Digital Audio Interface                                | 7  |

| 1.6.    | Control                                                | 7  |

| 1.7.    | Package                                                | 7  |

| 2. Func | tional Description                                     | 8  |

| 2.1.    | Video Processor                                        | 10 |

| 2.1.1   | . Supported Input Resolutions to Video Processing Core | 10 |

| 2.1.2   | 2. Special Considerations for 4K x 2K Inputs           | 10 |

| 2.1.3   | 8. Supported Output Resolutions                        | 10 |

| 2.1.4   | I. Video Processing Blocks                             | 10 |

| 2.1.5   | 5. Bypass Modes                                        | 12 |

| 2.1.6   | 5. Processing Mode                                     | 12 |

| 2.2.    | Input Preprocessing                                    | 12 |

| 2.2.1   | Picture Controls                                       | 12 |

| 2.2.2   | 2. 3 x 3 Matrix (Multicolor Space Converter)           | 13 |

| 2.2.3   | 8. Chroma Subsampler                                   | 13 |

| 2.3.    | Mosquito Noise Reduction                               | 13 |

| 2.4.    | Video Smoothing                                        | 13 |

| 2.5.    | Detail/Edge Enhancement                                | 13 |

| 2.6.    | Scaler                                                 | 14 |

| 2.7.    | Keystoning                                             | 14 |

| 2.8.    | Standalone Video Timing Generators                     | 14 |

| 2.9.    | Test Pattern Generator                                 | 15 |

| 2.10.   | On-screen Display                                      | 15 |

| 2.11.   | Output Postprocessing                                  | 15 |

| 2.11    | .1. Chroma Upsampler                                   | 15 |

| 2.11    | .2. 3 x 3 Matrix (Multicolor Space Converter)          | 15 |

| 2.12.   | 4:2:0 Output                                           | 15 |

| 2.13.   | HDMI Output                                            | 17 |

| 2.13    | .1. TMDS Transmitter Core                              | 17 |

| 2.13    | .2. Deep Color Support                                 | 17 |

| 2.13    | .3. Source Termination                                 | 17 |

| 2.13    | .4. HDCP Encryption Engine/XOR Mask                    | 17 |

| 2.13    |                                                        |    |

| 2.13    |                                                        |    |

| 2.13    | .7. DDC Master I <sup>2</sup> C Interface              | 18 |

| 2.13    | .8. Receiver Sense and Hot Plug Detection              | 18 |

| 2.13    | .9. Interrupts                                         | 18 |

| 2.14.   | HDMI Input                                             |    |

| 2.14    |                                                        |    |

| 2.14    |                                                        |    |

| 2.14    |                                                        |    |

| 2.14    |                                                        |    |

| 2.14    | .5. HDCP Embedded Keys                                 | 19 |

| 2.14    |                                                        |    |

| 2.15.   | Audio Input Processing                                 | 19 |

| 2.15    |                                                        |    |

| 2.15    | .2. Direct Stream Digital Input                        | 20 |

|    | 2.15.3.             | S/PDIF Input                                                       | .20        |

|----|---------------------|--------------------------------------------------------------------|------------|

|    | 2.15.4.             | Requirement for an MCLK                                            |            |

|    | 2.15.5.             | Audio Downsampler                                                  |            |

|    | 2.15.6.             | High-bitrate Audio on HDMI                                         |            |

|    | 2.15.7.             | I <sup>2</sup> S-to-SPDIF Conversion                               |            |

|    | -                   | Idio Output Processing                                             |            |

| 4  | 2.10. AU<br>2.16.1. | S/PDIF Output                                                      |            |

|    | 2.16.1.             |                                                                    |            |

|    | -                   | I <sup>2</sup> S Audio Output                                      |            |

|    | 2.16.3.             | One-bit Audio Output                                               |            |

|    | 2.16.4.             | High-bitrate Audio Support                                         |            |

|    | 2.16.5.             | Auto Audio Configuration                                           |            |

|    | 2.16.6.             | Soft Mute                                                          |            |

|    |                     | EC Interface                                                       |            |

|    |                     | PIO                                                                |            |

| 4  |                     | ontrol and Configuration                                           |            |

|    | 2.19.1.             | Register/Configuration Logic                                       |            |

|    | 2.19.2.             | I <sup>2</sup> C Serial Ports                                      | .24        |

|    |                     | SPI Serial Bus                                                     |            |

|    | 2.19.4.             | Delay from Reset Deactivation to Register Access                   |            |

| 2  | 2.20. Pi            | n Strapping                                                        | .25        |

| 2  | 2.21. Po            | ower Supply Sequencing                                             | .25        |

| 2  | 2.22. Au            | udio PLL Reset                                                     | .25        |

| 3. | Electrical          | Specifications                                                     | .26        |

| 3  | 3.1. Abso           | lute Maximum Conditions                                            | .26        |

| 3  | 3.2. Norr           | nal Operating Conditions                                           | .26        |

| 3  | 3.3. DC S           | pecifications                                                      | .27        |

|    | 3.3.1.              | DC Power Supply Pin Specifications                                 | .29        |

| 3  | 3.4. AC S           | pecifications                                                      | .29        |

| 3  | 3.5. Cont           | rol Timing Specifications                                          | .31        |

| 4. | Timing Di           | agrams                                                             | .33        |

| 2  | -                   | t Timing Diagrams                                                  |            |

| 2  |                     | S Input Timing Diagrams                                            |            |

| 2  |                     | al Audio Input Timing Diagrams                                     |            |

| 2  | -                   | al Audio Output Timing Diagrams                                    |            |

| 2  | -                   | rol Signal Timing Diagrams                                         |            |

|    | 4.5.1.              | I <sup>2</sup> C Timing Diagram                                    |            |

|    | -                   | SPI Timing Diagrams                                                |            |

| 2  |                     | ulating Setup and Hold Times for I <sup>2</sup> S Audio Output Bus |            |

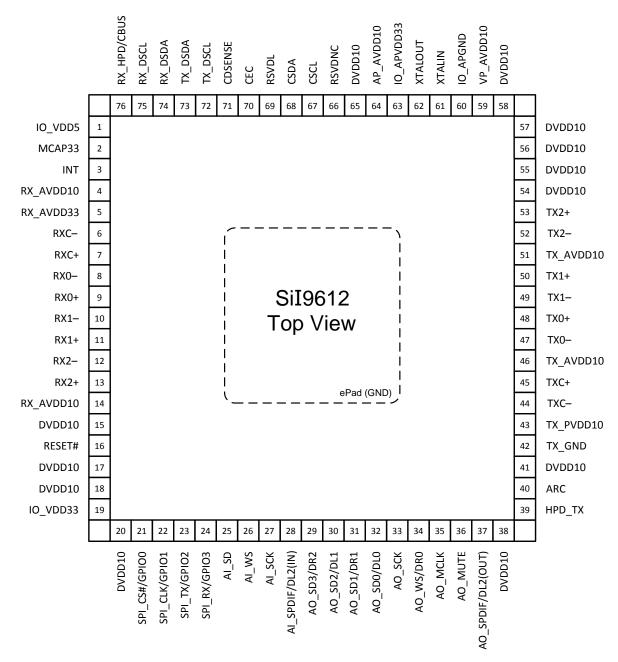

| 5. |                     | am and Pin Descriptions                                            |            |

| -  | -                   | Diagram                                                            |            |

|    |                     | Descriptions                                                       |            |

|    | 5.2.1.              | HDMI Receiver Control Signal Pins                                  |            |

|    | 5.2.2.              | HDMI Receiver Differential Signal Data Pins                        |            |

|    | 5.2.3.              | Digital Audio Output Pins                                          |            |

|    | 5.2.3.              | HDMI Transmitter TMDS Output Pins                                  |            |

|    | 5.2.4.              |                                                                    |            |

|    |                     | HDMI Transmitter Control Signal Pins                               |            |

|    | 5.2.6.              | Audio Input Pins                                                   |            |

|    | 5.2.7.              | Configuration/Programming Pins                                     |            |

|    | 5.2.8.              | Crystal Clock Pins                                                 |            |

|    | 5.2.9.              | Power and Ground Pins                                              |            |

|    | F 0 10              | Reserved Pins                                                      |            |

| ~  | 5.2.10.             |                                                                    |            |

| 6. | Feature I           | nformation                                                         | .44        |

|    | Feature I           |                                                                    | .44<br>.44 |

| 6.1.2.      | Local I <sup>2</sup> C Interface              | 45 |

|-------------|-----------------------------------------------|----|

| 6.1.3.      | Video Requirement for I <sup>2</sup> C Access | 46 |

| 6.1.4.      | Local SPI Serial Interface                    | 46 |

| 7. Packa    | ge Information                                |    |

| 7.1. e      | Pad Reguirements                              |    |

| 7.2. P      | PCB Layout Guidelines                         | 48 |

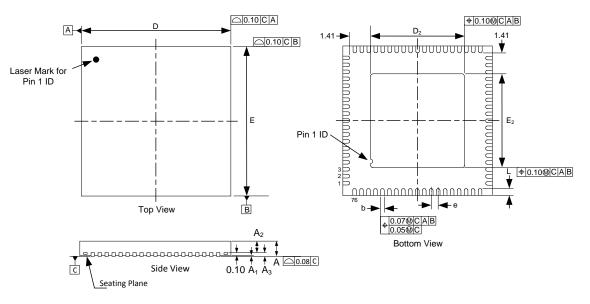

| 7.3. P      | Package Dimensions                            | 49 |

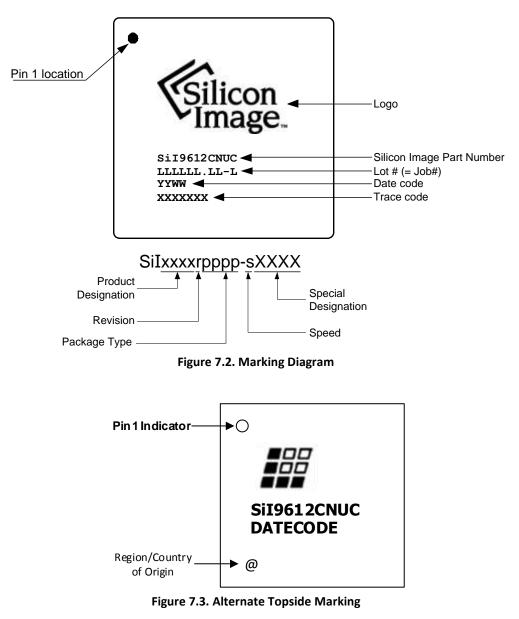

| 7.4. N      | Narking Specification                         |    |

| 7.5. C      | Ordering Information                          |    |

| References  | ····· ··· ····························        |    |

| Standard    | ds Documents                                  |    |

| Standard    | ds Groups                                     |    |

| Lattice S   | emiconductor Documents                        |    |

| Technica    | al Support                                    |    |

| Revision Hi | story                                         |    |

# **Figures**

| Figure 1.1. Typical Application                                                           | 7  |

|-------------------------------------------------------------------------------------------|----|

| Figure 2.1. Functional Video Path Block Diagram                                           |    |

| Figure 2.2. Audio Path Block Diagram                                                      | 9  |

| Figure 2.3. Video Processing Blocks                                                       |    |

| Figure 2.4. Bypass Options                                                                |    |

| Figure 2.5. Location of Cb/Cr with Respect to Y in YCbCr 4:2:0                            | 16 |

| Figure 2.6. YCbCr 4:2:0 Signal Mapping and Timing Diagram                                 |    |

| Figure 2.7. High-speed Data Transmission                                                  |    |

| Figure 2.8. High-bitrate Stream before and after Reassembly and Splitting                 | 21 |

| Figure 2.9. High-bitrate Stream after Splitting                                           | 22 |

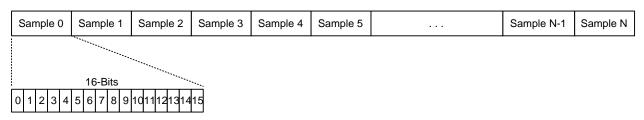

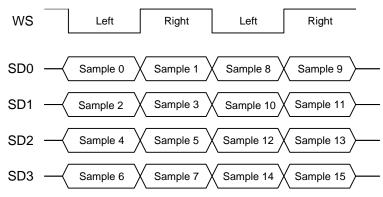

| Figure 2.10. Layout of High-bitrate Audio Samples on I <sup>2</sup> S                     |    |

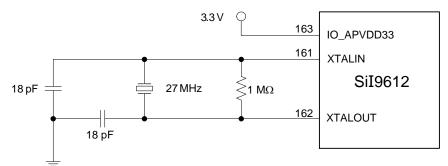

| Figure 3.1. Crystal Clock Schematic                                                       | 31 |

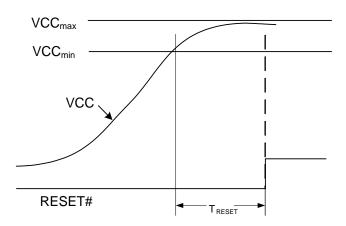

| Figure 4.1. Conditions for Use of RESET#                                                  | 33 |

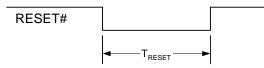

| Figure 4.2. RESET# Minimum Timing                                                         |    |

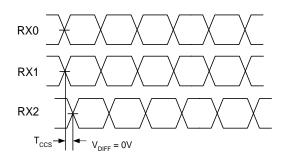

| Figure 4.3. TMDS Channel-to-Channel Skew Timing                                           | 33 |

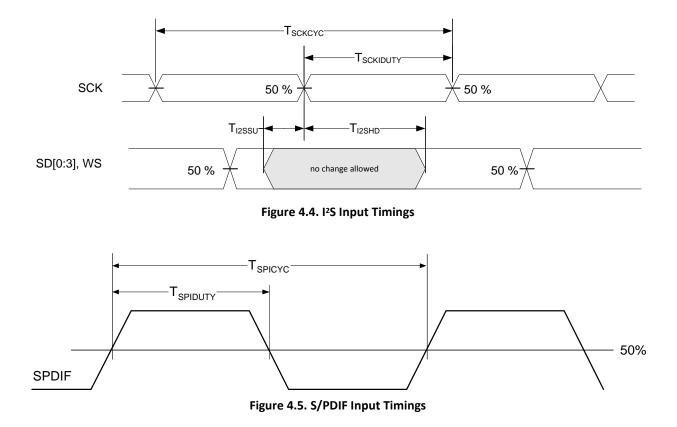

| Figure 4.4. I <sup>2</sup> S Input Timings                                                | 34 |

| Figure 4.5. S/PDIF Input Timings                                                          | 34 |

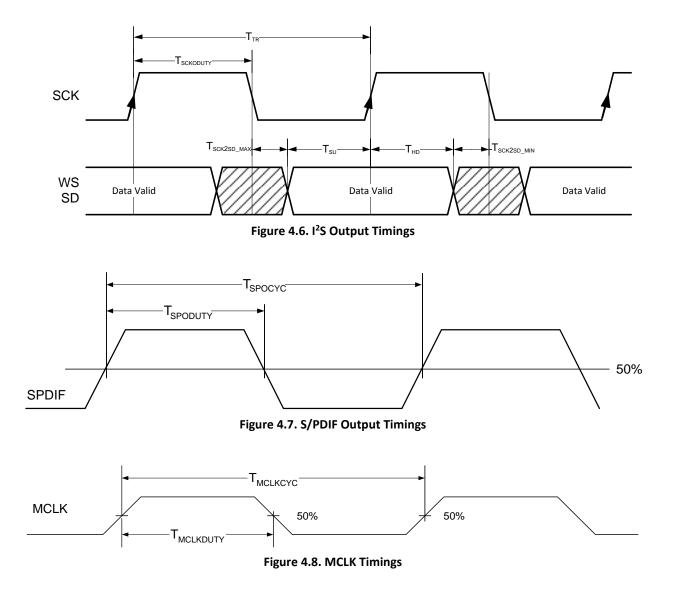

| Figure 4.6. I <sup>2</sup> S Output Timings                                               |    |

| Figure 4.7. S/PDIF Output Timings                                                         | 35 |

| Figure 4.8. MCLK Timings                                                                  |    |

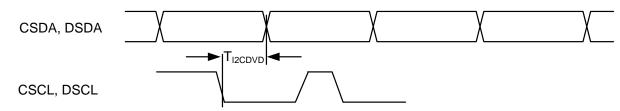

| Figure 4.9. I <sup>2</sup> C Data Valid Delay                                             |    |

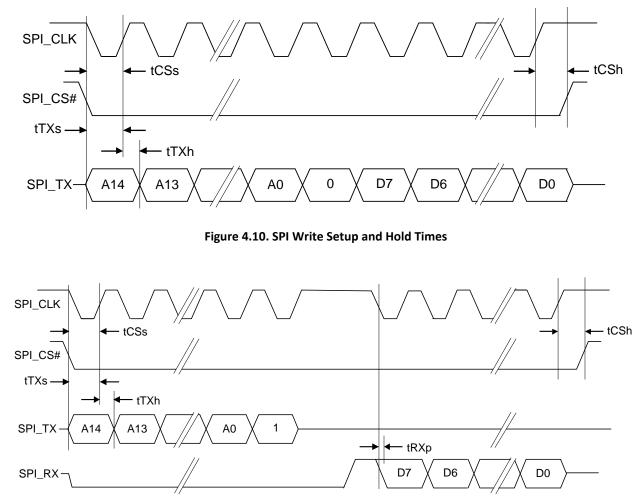

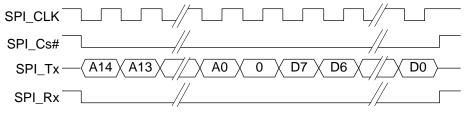

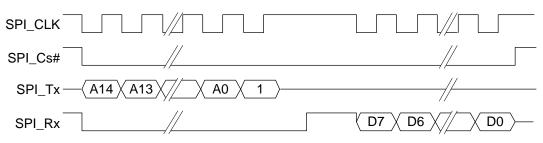

| Figure 4.10. SPI Write Setup and Hold Times                                               | 36 |

| Figure 4.11. SPI Read Setup and Hold Times                                                | 36 |

| Figure 5.1. Pin Diagram                                                                   |    |

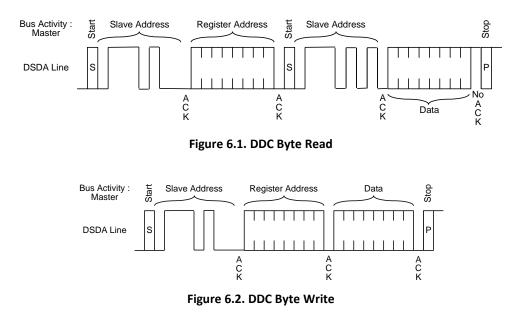

| Figure 6.1. DDC Byte Read                                                                 |    |

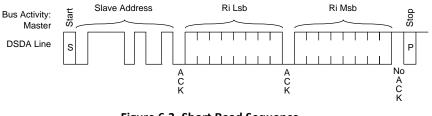

| Figure 6.2. DDC Byte Write                                                                |    |

| Figure 6.3. Short Read Sequence                                                           |    |

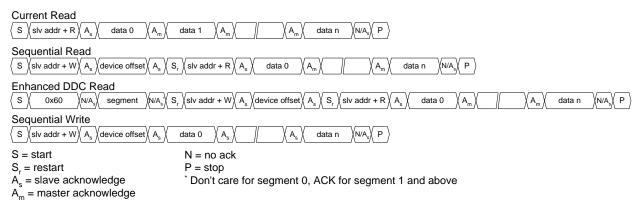

| Figure 6.4. DDC Master I <sup>2</sup> C Supported Transactions                            |    |

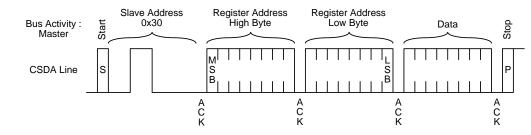

| Figure 6.5. Register Write Cycle on Local I <sup>2</sup> C                                |    |

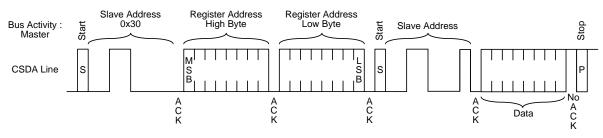

| Figure 6.6. Register Read Cycle on Local I <sup>2</sup> C                                 |    |

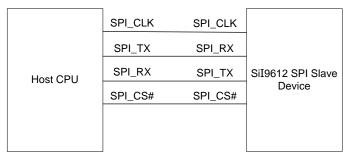

| Figure 6.7. SPI Serial Connection Example: Host $\leftrightarrow$ Single SPI Slave Device |    |

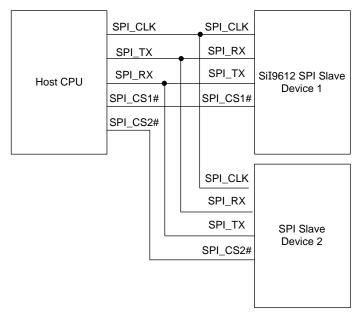

| Figure 6.8. SPI Serial Connection Example: Host $\leftrightarrow$ Dual SPI Slave Devices  |    |

| Figure 6.9: SPI Serial Write Operation                                                    |    |

| Figure 6.10: SPI Serial Read Operation                                                    |    |

| Figure 7.1. Package Diagram                                                               |    |

| Figure 7.2. Marking Diagram                                                               |    |

| Figure 7.3. Alternate Topside Marking                                                     | 50 |

# Tables

| Table 2.1. Audio Multiplexing Options                                        | 9  |

|------------------------------------------------------------------------------|----|

| Table 2.2. Multicolor Space Converter Input/Output Formats                   | 13 |

| Table 2.3. DSD Input Pin Mapping                                             | 20 |

| Table 2.4. Channel Status Bits Used for Word Length                          | 21 |

| Table 2.5. Supported MCLK Frequencies                                        | 22 |

| Table 2.6. DSD Output Pin Mapping                                            | 23 |

| Table 2.7. Pin Strapping Options                                             |    |

| Table 3.1. Absolute Maximum Conditions                                       | 26 |

| Table 3.2. Normal Operating Conditions                                       | 26 |

| Table 3.3. Digital I/O Specifications                                        |    |

| Table 3.4. TMDS Input DC Specifications – HDMI Mode                          |    |

| Table 3.5. TMDS Input DC Specifications – MHL Mode                           | 27 |

| Table 3.6. TMDS Output DC Specifications                                     |    |

| Table 3.7. Single Mode Audio Return Channel DC Specifications                |    |

| Table 3.8. CEC DC Specifications                                             |    |

| Table 3.9. CBUS DC Specifications                                            |    |

| Table 3.10. Total Power Dissipation                                          |    |

| Table 3.11. Power-down Mode Power Dissipation                                |    |

| Table 3.12. TMDS Input AC Timing Specifications – HDMI Mode                  |    |

| Table 3.13. TMDS Input AC Timing Specifications – MHL Mode                   |    |

| Table 3.14. TMDS Output AC Timing Specifications Mode                        |    |

| Table 3.15. CEC AC Specifications                                            |    |

| Table 3.16. CBUS AC Specifications                                           |    |

| Table 3.17. I <sup>2</sup> S Audio Input Port Timing Specifications          |    |

| Table 3.18. S/PDIF Input Port Timing Specifications                          |    |

| Table 3.19. I <sup>2</sup> S Audio Output Port Timing Specifications         |    |

| Table 3.20. S/PDIF Output Port Timing Specifications                         |    |

| Table 3.21. Crystal Clock Timings                                            |    |

| Table 3.22. Reset Timings                                                    | 31 |

| Table 3.23. I <sup>2</sup> C Control Signal Timings                          |    |

| Table 3.24. SPI Control Signal Timings                                       |    |

| Table 4.1. I <sup>2</sup> S Setup and Hold Time Calculations                 |    |

| Table 6.1. Control of Local I <sup>2</sup> C Device Address with AO_MUTE Pin | 46 |

# 1. General Description

The Lattice Semiconductor SiI9612 video processor supports High-definition Multimedia Interface (HDMI<sup>®</sup>) and video processing requirements for a Blu-ray Player/Recorder, Audio Video Receiver (AVR), and other video processors. It incorporates an integrated HDMI/Mobile High-definition Link 2 (MHL<sup>®</sup>) receiver and an HDMI transmitter that supports HDCP repeaters.

Lattice Semiconductor VRS<sup>®</sup> ClearView video processing enhances video streaming quality with noise reduction, Video Smoothing<sup>™</sup>, and picture enhancement. VRS<sup>®</sup> ClearView also includes a 4K adaptive scaler to drive the emerging 4K display market.

The Sil9612 device is preprogrammed with Highbandwidth Digital Content Protection (HDCP) keys for both receiver and transmitter, which helps reduce programming overhead and lowers manufacturing costs.

# 1.1. Video Processor

- Supports video input formats up to 1080p and UXGA including 4K x 2K pass-through

- Supports video output formats up to 1080p, WUXGA, and 4K x 2K

- Full 10-bit Adaptive Scaler

- Mosquito Noise Reduction

- Supports upscaling to 4K x 2K

- Supports downscaling from 1080p @ 60 Hz

- Video smoothing (pre- and postscaler)

- Detail and edge enhancement (prescaler)

- 12-bit preprocessing including color space conversion and picture control

- 12-bit postprocessing including color space conversion

- Picture controls

- Test Pattern Generator (TPG)

# 1.2. On-screen Display

- Character-based

- Supports On-screen Display (OSD) over 3D video

- Supports alpha-blending

#### 1.3. Video Input

- 300 MHz HDMI receiver port with 3D support

- MHL with 1080p @ 60 Hz support

### 1.4. Video Output

• 300 MHz HDMI transmitter port

#### 1.5. Digital Audio Interface

- Inputs

- I<sup>2</sup>S input with multichannel support

- S/PDIF input

- Audio Return Channel (ARC) input

- Outputs

- I<sup>2</sup>S output with four data signals for multichannel formats, and flexible programmable channel mapping including DSD

- High Bitrate Audio output including Dolby<sup>®</sup> TrueHD and DTS-HD Master Audio<sup>™</sup>

- S/PDIF output supports LPCM, Dolby Digital, DTS digital audio transmission with a 32 kHz – 192 kHz fs sample rate

- Intelligent audio mute capability avoids pops and noise with automatic soft mute and unmute

- IEC60958 or IEC61937 compatible

# 1.6. Control

- I<sup>2</sup>C and Serial Peripheral Interface (SPI) Bus

- DDC for HDMI receiver and transmitter

- Consumer Electronics Control (CEC) interface incorporates an HDMI CEC I/O and an integrated CEC Programming Interface (CPI)

# 1.7. Package

• 9 mm × 9 mm, 76 pin MQFN package with ePad

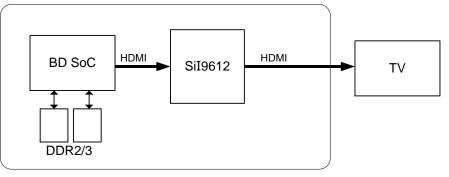

Figure 1.1. Typical Application

# 2. Functional Description

The Sil9612 video processor is ideally suited for Blu-ray players, A/V receivers, and video processing applications. It features a digital processing core that performs real-time video format conversion and image improvement. Format conversion is achieved through an innovative adaptive scaler that allows the device to upscale from any input format to 4K x 2K resolutions. Proprietary video processing algorithms improve the picture quality by removing unnaturally appearing noise or artifacts, smoothing edges and sharpening the image. Image improvement is supported for both standard and high-definition video.

An on-chip character generated On-screen Display (OSD), organized as 108 x 30 rows and columns, is included in the Sil9612 device. The OSD has split-screen mode to support display of the OSD over a 3D image.

The Sil9612 device provides a Test Pattern Generator (TPG) that is fully programmable by software and is able to generate test patterns without a valid input signal. With a maximum supported resolution of 4096 x 2208, it is able to generate test patterns for both 4K x 2K and 1080p 3D video output formats.

The Sil9612 video processor integrates a full 300 MHz HDMI receiver and HDMI transmitter. Mobile High-definition Link (MHL) technology is available on the HDMI receiver. The MHL receiver supports PackedPixel mode. The Audio Return Channel (ARC), provided for the HDMI transmitter port, allows the Sil9612 device to receive a S/PDIF signal from the connected DTV.

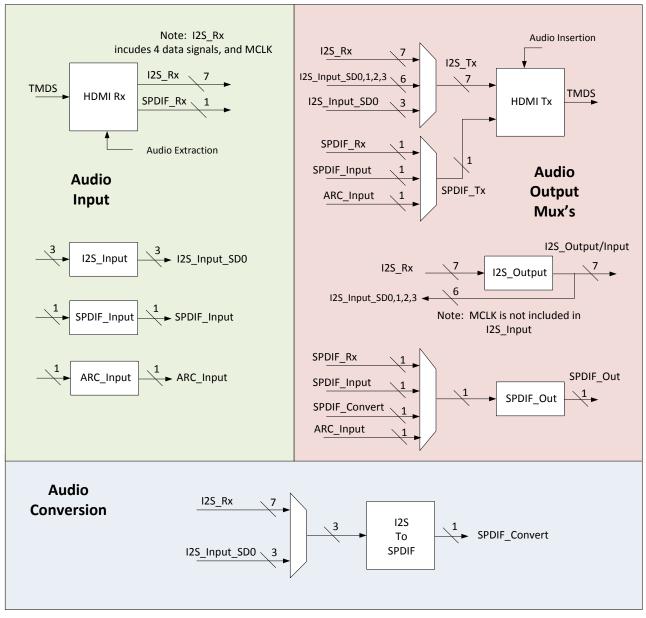

The Sil9612 video processor supports audio extraction and insertion. Audio extracted from the HDMI receiver can be output simultaneously to a S/PDIF port, a multichannel I<sup>2</sup>S port, and to the HDMI transmitter for repacketization. Audio to be transmitted on the HDMI output can be selected from one of four other sources: S/PDIF input, 2-channel I<sup>2</sup>S input, multichannel I<sup>2</sup>S input, and ARC input. The video processor can also convert the LPCM data received from the 2-channel I<sup>2</sup>S input or the I<sup>2</sup>S output of the HDMI receiver to an IEC60958 stream to output on the S/PDIF port.

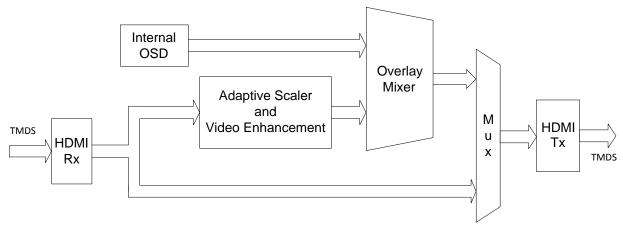

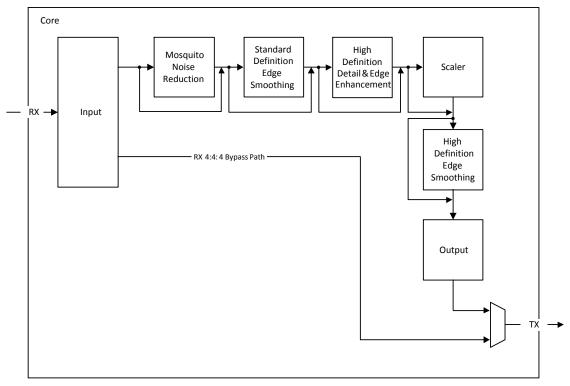

Figure 2.1 below and Figure 2.2 on the next page show the functional blocks of the chip.

Figure 2.1. Functional Video Path Block Diagram

Figure 2.2. Audio Path Block Diagram

Table 2.1 summarizes the audio outputs that are available with each audio input.

| Audio Input   | Audio Output                  |            |               |             |  |  |

|---------------|-------------------------------|------------|---------------|-------------|--|--|

| Addio Input   | SPDIF_Out                     | I2S_Output | HDMI SPDIF_Tx | HDMI I2S_Tx |  |  |

| SPDIF_Input   | Supported                     | _          | Supported     | _           |  |  |

| I2S_Input     | Supported (2-channel formats) | Supported  | —             | Supported   |  |  |

| HDMI SPDIF_Rx | Supported                     | _          | Supported     | _           |  |  |

| HDMI I2S_Rx   | Supported (2-channel formats) | Supported  | _             | Supported   |  |  |

| ARC_Input     | Supported                     |            | Supported     | _           |  |  |

<sup>© 2012-2017</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# 2.1. Video Processor

The Sil9612 video processor features the latest VRS® technologies from Lattice Semiconductor including a 4K Adaptive Scaler, Video Smoothing, enhanced Mosquito Noise Reduction, and Detail and Edge Enhancement. These technologies improve the picture quality of highly compressed video sources by enhancing resolution through scaling and removing video noise without side effects. Adaptive scaling delivers automatically optimized performance for all sources including internet video, high-definition video, and computer graphics. All processing resources are included on-chip and external RAM is not required.

#### 2.1.1. Supported Input Resolutions to Video Processing Core

The Sil9612 video processing core supports several input formats as defined in the CEA-861E Specification. It also supports several PC formats. Supported formats include, but are not limited to, the following:

- 720 x 480i

- 720 x 576i

- 1440 x 480i

- 1440 x 576i

- 720 x 480p

- 720 x 576p

- 1280 x 720p50

- 1280 x 720p60

- 1920 x 1080i50 .

- 1920 x 1080i60

- 1920 x 1080p50

- 1920 x 1080p60

- VGA

- SVGA

- XGA

- SXGA

UXGA

•

- 4K x 2K @ 23.98 Hz, 24 Hz, 25 Hz, 29.97 Hz, and 30 Hz passthrough

- 4K x 2K YCbCr 4:2:0 @ 59.94 Hz, 60 Hz, and 50 Hz pass-through

- 1080p resolutions may require a small amount of vertical zoom when scaling down to certain SD resolutions.

The Sil9612 video processor does not support frame rate conversion. The output frame rate always needs to be the same as the input frame rate.

# 2.1.2. Special Considerations for 4K x 2K Inputs

4K x 2K inputs must bypass all major processing blocks. In this mode, color space conversion and picture controls are still available. The exception is YCbCr 4:2:0 encoded 4K x 2K @ 60 Hz (59.94 Hz) and 50 Hz inputs, in which color space conversion and picture controls must also be bypassed.

Figure 2.4 on page 12 shows the bypass modes available on the Sil9612 video processor.

# 2.1.3. Supported Output Resolutions

The Sil9612 video processing core supports several output formats including the following:

.

.

480i

480p

576i

576p

720p

1080i 1080p

VGA

SVGA

- •

- XGA •

- 4K x 2K @ 23.98 Hz, 24 Hz, 25 Hz, 29.97 Hz, and 30 Hz

- 4K x 2K YCbCr 4:2:0 @ 59.94 Hz, 60 Hz, 50 Hz

SXGA

UXGA

•

The Sil9612 device does not support frame rate conversion. The output frame rate always needs to be the same as the input frame rate.

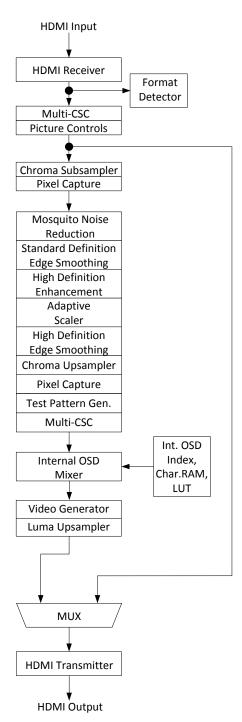

# 2.1.4. Video Processing Blocks

The Sil9612 video processor contains the following video processing blocks:

- Input Preprocessing reformats the input signal to YCbCr 4:2:2 format

- **Mosquito Noise Reduction**

- Standard Definition Edge Smoothing

- High-definition Detail and Edge Enhancement

- Adaptive Video Scaling

- **High-definition Edge Smoothing**

- **Test Pattern Generation**

- Internal OSD Blending

- Output Postprocessing reformats the video data to many different output formats

10

Figure 2.3 shows a block diagram indicating the placement of these blocks in the video path.

Figure 2.3. Video Processing Blocks

<sup>© 2012-2017</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

#### 2.1.5. Bypass Modes

The Sil9612 device provides two options for bypassing the internal processing blocks using control registers that are described in the Sil9612 programmer's reference (*Sil-PR-1069; requires NDA with Lattice Semiconductor*). Figure 2.4 shows the available bypass options.

Figure 2.4. Bypass Options

#### 2.1.6. Processing Mode

In processing mode, the output of the Sil9612 video processor can be in RGB or YCbCr mode. Multiple color space converters, chroma upsampler, and chroma downsampler logic blocks are available on the input and output of the processing block to ensure support for a wide range of applications.

# 2.2. Input Preprocessing

The Sil9612 video processor provides a number of video processing functions that can be used to adjust the incoming video signal before it is sent to the scaler and enhancement blocks. These functions are color space conversion, picture controls, and chroma subsampling. All processing is done in 36 bits.

#### 2.2.1. Picture Controls

Picture controls are used to adjust the following aspects of the video input signal:

- Input Black Level: 4096 levels of black level control.

- Contrast: 1 integer bit, 8 fractional bits. Range is from 0 to 1.996 with a 1/256 resolution for a total of 512 levels of contrast control.

- Saturation:1 integer bit, 8 fractional bits. Range is from 0 to 1.996 with a 1/256 resolution for a total of 512 levels of saturation control.

### 2.2.2. 3 x 3 Matrix (Multicolor Space Converter)

In addition to the built-in picture controls, the Sil9612 device features a 3 x 3 matrix module at the input path. These can be used as programmable linear control to adjust the brightness, contrast, saturation, and hue in the three components of the input signal. It can also be used to perform RGB-to-YCbCr and YCbCr-to-RGB color space conversions.

The 3x3 matrix also comes with 64 sets of predefined coefficients to support all standard color space conversions. Table 2.2 shows the eight possible formats available for the input and output of the 3 x 3 matrix.

| Tuble 2.2. Multicolor Space converter input/output ronnats |        |             |  |  |  |  |

|------------------------------------------------------------|--------|-------------|--|--|--|--|

| Color Space                                                | Levels | Colorimetry |  |  |  |  |

| YCbCr                                                      | Video  | 709         |  |  |  |  |

| YCbCr                                                      | Video  | 601         |  |  |  |  |

| YCbCr                                                      | PC     | 709         |  |  |  |  |

| YCbCr                                                      | РС     | 601         |  |  |  |  |

| RGB                                                        | Video  | 709         |  |  |  |  |

| RGB                                                        | Video  | 601         |  |  |  |  |

| RGB                                                        | PC     | 709         |  |  |  |  |

| RGB                                                        | PC     | 601         |  |  |  |  |

|                                                            |        |             |  |  |  |  |

Table 2.2. Multicolor Space Converter Input/Output Formats

#### 2.2.3. Chroma Subsampler

The chroma subsampler module converts YCbCr 4:4:4 input signals to YCbCr 4:2:2 format.

# 2.3. Mosquito Noise Reduction

The Sil9612 video processor detects and removes mosquito noise. Mosquito noise is a common compression artifact caused by MPEG decoders, and is often exhibited around the edges of text and computer generated graphics. The Sil9612 algorithm detects areas where mosquito noise would be the most likely, and then works to diminish the mosquito noise without blurring the edge of the text or graphic. The maximum resolution supported by mosquito noise reduction is 576p.

# 2.4. Video Smoothing

The Lattice Semiconductor Video Smoothing technology removes the rough edges in an image, such as the staircase appearance of a diagonal line drawn on the screen without edge smoothing (stair stepped effect). Digital compression, scaling artifacts, poor quality deinterlacing, or resolution limitations in the digital sampling of an image cause these effects. Smoothing technology creates the effect of a high resolution image without softening the entire image.

The Sil9612 device offers two smoothing blocks. The Standard Definition Edge Smoothing block comes before the scaler block and removes any rough edges on the original image. The High-definition Edge Smoothing block comes after the scaler and it reduces rough edges caused by upscaling the video.

# 2.5. Detail/Edge Enhancement

There are two types of sharpening in the SiI9612 device: general and edge-qualified. Sharpening is done before scaling in the High-definition Enhancement block. The High-definition Enhancement block works well for sharpening both SD and HD video.

Detail enhancement can be used to increase fine detail or reduce noise for overly enhanced images. Detail enhancement is controlled with an 8-bit signed register. Positive control numbers from 1 to 127 increase sharpening and negative numbers in two's complement format decrease sharpening. This means that if the control word is negative, the image is low-pass filtered. The control register defaults to 0, which does not apply any sharpening.

Edge enhancement can be used to sharpen edges or reduce overly enhanced edges. The edge qualified sharpening or edge enhancement works only on object edges. It also uses an 8-bit signed control word, like general sharpening, so

<sup>© 2012-2017</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

sharpening can increase around object edges if the control word is positive, and edges of objects can be filtered if the control word is negative. There is a *clipping* control for edge-qualified sharpening that allows for adjustment of edge sensitivity. The clipping control is also an 8-bit number, but it is unsigned. The clipping control allows the user to select the strength of object edges to which sharpening is applied.

The detail enhancement and edge-qualified enhancement methods are additive, so the results of both sharpening methods are combined.

An example of this would be to use general sharpening to increase detail in the entire image. If object edges are overenhanced, then negative edge qualified sharpening is applied to reduce the overenhancement of the edges.

If general sharpening is applied to a noisy image, the increase in noise may be objectionable. In that case, positive edge qualified sharpening should be applied to sharpen object edges, but not increase the noise level.

# 2.6. Scaler

The scaler provides format conversion capability to the SiI9612 video processor. It reads the input data from internal line memory and applies horizontal and vertical scaling. Adaptive scaling ensures that the converted format is free of ringing artifacts regardless of content, whether video, graphic, or a mix of both. Format conversion is supported for both video and PC formats.

The scaler does not support a frame buffer. The output frame rate is locked to the input frame rate. A small amount of vertical zoom is necessary when scaling down from 1080p resolutions to some SD resolutions such as 480p.

The scaler can perform scaling on a limited set of Frame Packed 3D formats. The only 3D format conversions that work are conversions from 720p Frame Packed to 1080p Frame Packed, or from 1080p Frame Packed to 720p Frame Packed.

The scaler supports panorama mode that changes the aspect ratio of the image. It can be used to fit a 4:3 SD image into a 16:9 HD format with minimal distortion. This is achieved by keeping the original image aspect ratio in the center of the scaled image, and gradually stretching the image towards its left and right edges. This results in no distortion at the image center while horizontal distortion gradually increases towards the left and right edges of the image. The panorama mode features an enhanced algorithm that reduces the distortion at the far edges of the image.

The scaler also includes both a border generator and a mask generator. The border generator is used to create a grey frame about the video image whereas the mask generator can be used to create a black frame around the border. Borders provide another method for correcting the aspect ratio of the displayed image, such as displaying a 4:3 image on a 16:9 frame without horizontal distortion by adding appropriately sized pillars on the left and right side of the image.

Other functions supported by the scaler block include Y/C delay that allows a horizontal offset between the chroma and luma signal to compensate for delay differences caused by other parts of the system, automatic Chroma Upsampling Error (CUE) correction, which detects chroma data that has been upsampled incorrectly in the vertical direction and suppresses the visual artifacts caused by these errors, and user-defined zoom and pan functions.

Scaler processing is done in YCbCr 4:2:2, 20-bit (10 bits per component) color space format.

# 2.7. Keystoning

The Sil9612 device supports Keystoning. Keystoning is necessary when an image is projected onto a surface at an angle resulting in a distorted image of a trapezoid. For example, if a projector is lower than the surface onto which it is projecting, the image is larger at the top than at the bottom.

# 2.8. Standalone Video Timing Generators

The Sil9612 device features a standalone Video Timing Generator (VTG) which allows it to generate a solid colored screen with any output format supported by the device. For example, a 1080p signal which produces a solid blue screen can be output when there are no inputs to the video processor.

The input clock for the VTG can be selected from among these clock sources: 27 MHz system clock, HDMI input clock and internal video PLLs.

<sup>© 2012-2017</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# 2.9. Test Pattern Generator

The Sil9612 video processor has a programmable Test Pattern Generator (TPG). The TPG is flexible and under software control. It is able to generate test patterns without a valid input signal. The maximum output resolution of the TPG is 4096 x 2208. The 4096 horizontal resolution supports all 4K x 2K formats. The 2208 vertical resolution supports Frame Packed 3D formats up to 1080p.

The TPG operates in YCbCr 4:4:4 color space format at 12 bits per color component.

# 2.10.On-screen Display

The Sil9612 video processor comes with a built-in character-based On-screen Display (OSD). The OSD is organized as a 108 x 30 character map that can be positioned anywhere on the screen. 384 characters can be created at 12 x 24 pixels per character or 192 characters at 24 x 24 pixels per character. The OSD can support transparency and a maximum of 64 pairs of foreground and background colors. The maximum resolution of the OSD is 1296 x 720 pixels.

The OSD supports a split mode that allows it to be overlaid onto some 3D video formats. The OSD can be split vertically or horizontally. When split vertically the OSD can be overlaid onto Frame Packed 3D formats or Top-and-Bottom 3D formats. When split horizontally, the OSD can be overlaid onto Side-by-Side 3D formats. However, 3D processing downstream from the Sil9612 device of Side-by-Side (Half) and Top-and-Bottom formats will distort the characters as they will be expanded by 2x horizontally in a Side-by-Side (Half) format, or they will be expanded by 2x vertically in a Top-and-Bottom format.

2x, 3x, and 4x pixel and line replication are supported for increasing the size of the OSD characters. Pixel replication is independent for horizontal and vertical. Pixel and line replication may be used to increase the legibility of the OSD for 4K x 2K output.

The OSD is rendered in YCbCr 4:4:4 or RGB color space.

# 2.11. Output Postprocessing

Additional processing can be performed on the output data after the scaling/enhancement data path before it is sent to the HDMI transmitter. These functions are color space conversion and chroma upsampling. All processing is done in 36 bits.

#### 2.11.1. Chroma Upsampler

The chroma upsampler module converts YCbCr 4:2:2 input signals to YCbCr 4:4:4 format.

#### 2.11.2.3 x 3 Matrix (Multicolor Space Converter)

The 3 x 3 matrix module is the same as the one in the input path. It performs color space conversion using a userprogrammed coefficient and offset values, or 64 predefined sets of coefficients for all standard color space conversions.

# 2.12.4:2:0 Output

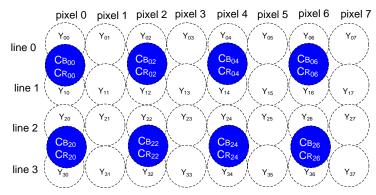

The Sil9612 video processor supports YCbCr 4:2:0 ready displays. The primary purpose of this pixel encoding format is to support the transmission of 4K x 2K @ 50/60 Hz formats using a link clock rate that is half the pixel clock rate, or 297 MHz, by reducing the bandwidth through chroma subsampling.

In YCbCr 4:2:0 format, the chroma components, Cb and Cr, are subsampled both horizontally and vertically with respect to the Y component by a factor of two. This produces a Y-to-Cb/Cr ratio of 4:1, which results in half the bandwidth of YCbCr 4:4:4 format. As shown in Figure 2.5 on the next page, the subsampled Cb and Cr components are co-sited and aligned with Y horizontally, but are shifted by half a line vertically.

Figure 2.5. Location of Cb/Cr with Respect to Y in YCbCr 4:2:0

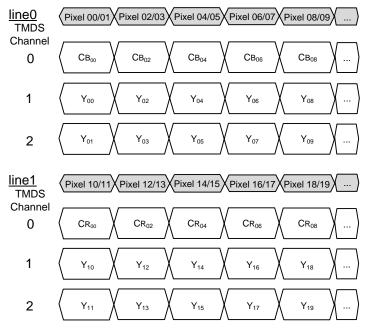

Figure 2.6 illustrates the organization and timing of the Y, Cb and Cr samples when transported across the HDMI link in YCbCr 4:2:0 format. Two horizontally successive Y samples are transmitted in TMDS channel 1 and 2 in order, respectively. The Cb and Cr samples are transmitted on alternate lines in TMDS channel 0, with Cb being transferred first.

Figure 2.6. YCbCr 4:2:0 Signal Mapping and Timing Diagram

The Sil9612 video processor provides a special mode for scaling any input format with 50/60 Hz frame rate to 4K x 2K @ 50/60 Hz in 4:2:0 output format. In this mode the scaler is configured to scale the input vertically to the full 4K x 2K vertical resolution of 2160 lines and horizontally to half the horizontal resolution, either 1920 or 2048 pixels. A half line vertical shift is then applied to the chroma component of the generated signal before being upsampled by a factor of two. The resultant 4:4:4 signal then goes to a luma upsampler module where the luma component is upsampled to create two times the number of samples. In the final stage, the luma component is sent out in two pixels per clock while the chroma components Cb and Cr are clocked out on alternating lines. All processing is done with an output clock of 297 MHz.

# 2.13.HDMI Output

The Sil9612 video processor features an HDMI transmitter with 300 MHz TMDS core for 1080p @ 60 Hz 3D and 4K x 2K outputs, full digital video and audio pipelines, integrated HDCP keys and encryption engine, and Audio Return Channel (ARC) input.

#### 2.13.1. TMDS Transmitter Core

The TMDS transmitter core performs 8-bit-to-10-bit TMDS encoding on the data received from the HDCP XOR mask, and is then sent over three TMDS data and one TMDS clock differential lines. See the HDCP Encryption Engine/XOR Mask on page 17 for more details.

The transmitter core supports link clocks from 25 MHz to 300 MHz. The internal PLL has the option to multiply the pixel clock to implement deep color or pixel repetition modes.

#### 2.13.2. Deep Color Support

The Sil9612 video processor provides support for deep color video data up to the maximum specified link speed of 3 Gb/s (300 MHz internal clock rate for the deep color packetized data). It supports 30-bit and 36-bit video input formats, and converts the data to 8-bit packets for encryption and encoding for transferring across the TMDS link.

When the input data width is wider than desired, the device can be programmed to dither or truncate the video data to the desired size. For example, if the input data width is a 12 bits per pixel component, but the sink device only supports 10 bits, the HDMI transmitter can be programmed to dither or truncate the 12-bit input data to the desired 10-bit output data.

#### 2.13.3. Source Termination

TMDS transmitters use a current source to develop the low-voltage differential signal at the receiver end of the DC-coupled TMDS transmission line, and constitute open termination for reflected waveforms. As a result, signal reflections created by traces, packaging, connectors, and the cable can arrive at the transmitter with increased amplitude.

To reduce these reflections, the HDMI transmitter port has an internal termination option of  $150 \Omega$  for single-ended termination, and  $300 \Omega$  for differential termination. This termination reduces the amplitude of the reflected signal, but it also lowers the common mode input voltage at the sink. Lattice Semiconductor recommends turning internal source termination off when the transmitter operates less than or equal to 165 MHz, and turning it on for frequencies above 165 MHz.

#### 2.13.4. HDCP Encryption Engine/XOR Mask

The HDMI transmitter provides an HDCP encryption engine that contains the logic necessary to encrypt the incoming audio and video data, and includes support for HDCP authentication and repeater checks. The system microcontroller controls the encryption process by using a set sequence of register reads and writes. An algorithm uses HDCP keys and a Key Selection Vector (KSV), stored in the HDCP key ROM to calculate a number that is then applied to an XOR mask. This process encrypts the audio and video data on a pixel-by-pixel basis during each clock cycle.

#### 2.13.5. HDCP Key ROM

The Sil9612 video processor comes preprogrammed with a set of production HDCP keys for the HDMI transmitter. The keys are stored in an internal ROM. System manufacturers do not need to purchase key sets from the Digital Content Protection LLC. Lattice Semiconductor handles all purchasing, programming, and security for the HDCP keys. The preprogrammed HDCP keys provide the highest level of security because there is no way to read the keys once the device is programmed.

Customers must sign the HDCP license agreement (<u>www.digital-cp.com</u>) or be under a specific NDA with Lattice Semiconductor before receiving Sil9612 samples.

#### 2.13.6. Audio Return Channel

The Sil9612 video processor provides an Audio Return Channel (ARC) input to receive an IEC60958-1 or IEC61937 audio stream from the connected sink device through the utility pin of the HDMI cable.

The Sil9612 device supports only single mode ARC. The Sil9612 ARC input can be made compatible for common mode ARC by using an AC-coupling network between the HPD and utility pins of the HDMI connector of the HDMI output port and the Sil9612 ARC pin.

#### 2.13.7. DDC Master I<sup>2</sup>C Interface

The Sil9612 HDMI transmitter includes a DDC master I<sup>2</sup>C interface for direct connection to the HDMI cable. The DDC master I<sup>2</sup>C interface is used for two purposes:

- To read the EDID of the connected downstream device,

- To perform HDCP authentication of the connected downstream device.

The host uses the DDC master logic to read the EDID by programming the target address, offset, and number of bytes. When completed, or when the DDC master FIFO becomes full, an interrupt signal is sent to the host so that the host can read data out of the FIFO.

The TPI hardware uses the DDC master to carry out HDCP authentication tasks. The request to perform HDCP authentication is initiated by the host, but it does not access the DDC master directly.

#### 2.13.8. Receiver Sense and Hot Plug Detection

The HDMI transmitter can detect a connected device through the Hot Plug Detect (HPD) input signal or the internal Receiver Sense (RSEN) logic. When HIGH, the HPD signal indicates to the transmitter that the EDID of the connected receiver is readable. The RSEN can be used to detect whether the attached device is powered by sensing the termination in the attached device. An interrupt can be generated whenever there is a change in the state of the HPD or RSEN signal.

#### 2.13.9. Interrupts

The Interrupt logic in the HDMI transmitter buffers interrupt events from different sources. Receiver Sense and Hot Plug Interrupts are also available in power-down mode. The logic for handling these interrupts when all clocks are disabled is also part of this block. The INT pin provides an interrupt signal to the system microcontroller when any of the following occur:

- Monitor Detect (either from the HPD input level or from the receiver sense feature) changes

- VSYNC (useful for synchronizing a microcontroller to the vertical timing interval)

- Error in the audio format

- DDC FIFO status changes

- HDCP authentication error

#### 2.14.HDMI Input

The Sil9612 video processor integrates an HDMI receiver that accepts 300 MHz inputs such as 1080p @ 60 Hz 3D and 4K x 2K video formats. It offers a full video and audio processing pipeline, integrated HDCP keys, and a decryption engine. MHL mode is available with support for PackedPixel mode.

#### 2.14.1. TMDS Receiver Core

The HDMI receiver core is the latest generation core and can receive TMDS data up to 300 MHz. The core performs 10to 8-bit TMDS decoding on the video data, and 10- to 4-bit TMDS decoding on the audio data received from the three TMDS differential data lines, along with a TMDS differential clock. The TMDS core can sense a stopped clock or stopped video and software can put the video processor into power down mode.

Adaptive equalization is applied to the input signal to counter high-frequency attenuation resulting from long cables, thus ensuring reliable data recovery.

<sup>© 2012-2017</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

The receiver core operates in either HDMI or MHL mode. In MHL mode, the receiver core demultiplexes a single TMDS data channel into its three component logical channels (two for PackedPixel mode) of 8 bits each using a common mode clock signal carried on the same TMDS channel.

#### 2.14.2. Deep Color Support

The Sil9612 video processor detects deep color packets in the HDMI data stream and automatically decodes the proper pixel clock setting and output bus width. The deep color mode can be read from registers as 24 bits, 30 bits, or 36 bits per pixel, up to 1080p @ 60 Hz. An interrupt can be generated whenever the deep color mode changes.

#### 2.14.3. MHL Receiver

The HDMI input of the Sil9612 video processor can be configured as a Mobile High-definition Link (MHL) receiver. When an MHL source is connected, an MHL cable detect sense signal from the cable is asserted and sent to the Sil9612 device, and also to the host microcontroller as an interrupt to configure the receiver port as an MHL port, and to prepare for the CBUS discovery process.

The MHL receiver supports PackedPixel mode, which encodes YCbCr 4:2:2 pixel data using 16 bits per pixel rather than 24 bits per pixel as in the other pixel encoding modes. The incoming pixel clock rate may be as high as 150 MHz in this mode, with a link clock rate of half of the pixel clock, which allows MHL to support 1080p @ 60 Hz video. The maximum link clock rate remains 75 MHz in PackedPixel mode.

#### 2.14.4. HDCP Decryption Engine/XOR Mask

The HDMI receiver provides an HDCP decryption engine to decrypt protected audio and video data transmitted by the source device. Decryption is enabled only after the successful completion of an authentication protocol between the source device and the HDMI receiver. This process is driven by the source device through a set sequence of read and writes through the DDC channel. A resulting calculated value is applied to an XOR mask during each clock cycle to decrypt the audio-visual data.

The HDMI receiver also contains all the necessary logic to support full HDCP repeaters. The KSV FIFO can store a KSV list consisting of up to 16 devices.

#### 2.14.5. HDCP Embedded Keys

The Sil9612 device is preprogrammed with a set of production HDCP keys for the HDMI receiver. The keys are stored on the chip in nonvolatile memory. Lattice Semiconductor handles all purchasing, programming, and security for the HDCP keys. Before receiving samples of the Sil9612 video processor, customers must sign the HDCP license agreement (available from Digital Content Protection LLC) or a special NDA with Lattice Semiconductor.

#### 2.14.6. EDID RAM Block

An EDID block is supported on the HDMI receiver port. The EDID block consists of 256 bytes of RAM to contain the EDID data structure. This memory, comprised of SRAM, is volatile and must be initialized by software during power up.

# 2.15. Audio Input Processing

The Sil9612 video processor provides multiple ways to accept digital audio signals for insertion onto the HDMI output stream. The HDMI transmitter receives the audio stream through an I<sup>2</sup>S or S/PDIF port. Audio data can come from one of many sources for each interface, controlled by a multiplexer. This is illustrated in Figure 2.2 on page 9.

All major audio encoding formats are supported, including LPCM audio, one-bit audio, and bitstream audio formats including high-bitrate audio.

#### 2.15.1. I<sup>2</sup>S Audio Input

There are two external I<sup>2</sup>S ports on the Sil9612 device. The first I<sup>2</sup>S port is comprised of three signal pins: AI\_SCK, AI\_WS, and AI\_SD. The signal pins are dedicated inputs intended to support 2-channel linear pulse code modulation (LPCM) audio. This I<sup>2</sup>S input port accepts audio sample frequencies of 32, 44.1, 48, 88.2, 96, 176.4, and 192 kHz.

The second I<sup>2</sup>S port has seven signal pins: AO\_MCLK, AO\_SCK, AO\_WS, and AO\_SD[3:0]. All pins except AO\_MCLK are bidirectional. The direction of these pins is controlled by a software programmable register. These pins default to

<sup>© 2012-2017</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

outputs. When the pins are configured as inputs, they enable an input of up to eight channels of LPCM audio for insertion onto the HDMI output. The I<sup>2</sup>S input supports sampling frequencies of 32 to 192 kHz.

The multichannel I<sup>2</sup>S interface also supports high-bitrate audio formats like Dolby<sup>®</sup> TrueHD and DTS-HD Master Audio<sup>™</sup>.

Only one of the I<sup>2</sup>S ports can be selected to send audio data to the HDMI transmitter at any given time.

#### 2.15.2. Direct Stream Digital Input

Seven pins are used for the Direct Stream Digital (DSD) interface that provides 6-channel one-bit audio data. This interface is for Super Audio Compact Disc (SACD) applications. The DSD input pins are mapped to the multichannel I<sup>2</sup>S pins and the S/PDIF input pin of the Sil9612 device as shown in Table 2.3 below.

The one-bit audio inputs are sampled on the positive edge of the DSD clock, assembled into 56-bit packets, and mapped to the appropriate FIFO. The Audio InfoFrame, instead of the Channel Status bits, carries the sampling information for one-bit audio. The one-bit audio interface supports input clock frequencies of 2.822 MHz (64 • 44.1 kHz) and 5.645 MHz (64 • 88.2 kHz).

| DSD Signal | Pin # | Pin Name |  |

|------------|-------|----------|--|

| DCLK       | 33    | AO_SCK   |  |

| DR0        | 34    | AO_WS    |  |

| DL0        | 32    | AO_SD0   |  |

| DR1        | 31    | AO_SD1   |  |

| DL1        | 30    | AO_SD2   |  |

| DR2        | 29    | AO_SD3   |  |

| DL2        | 28    | AI_SPDIF |  |

#### 2.15.3. S/PDIF Input

The Sil9612 device can accept digital audio from a S/PDIF input pin. The Sony/Philips Digital Interface Format (S/PDIF) interface is usually associated with compressed audio formats such as Dolby<sup>®</sup> Digital (AC-3), DTS, and the more advanced variants of these formats. The S/PDIF interface also supports the LPCM format at sampling frequencies of 32 kHz, 44.1 kHz, 48 kHz, 88.2 kHz, 96 kHz, 176.4 kHz, and 192 kHz.

#### 2.15.4. Requirement for an MCLK

The video processor includes an integrated MCLK generator for operation without requiring an external clock PLL. This removes the requirement for an MCLK input on the device for creating the time stamp value used in audio clock recovery.

#### 2.15.5. Audio Downsampler

The Sil9612 device has an audio downsampler function that downsamples the incoming two-channel audio data and sends the result over the HDMI link. The audio data can be downsampled by one-half or one-fourth with register control. Conversions from 192 kHz to 48 kHz, 176.4 kHz to 44.1 kHz, 96 kHz to 48 kHz, and 88.2 kHz to 44.1 kHz are supported. Some limitations in the audio sample word length, when using this feature, may need special consideration in a real application.

When enabling the audio downsampler, the Channel Status registers for the audio sample word lengths sent over the HDMI link always indicate the maximum possible length. For example, if the input S/PDIF stream was in 20-bit mode with 16 bits valid after enabling the downsampler, the Channel Status indicates 20-bit mode with 20 bits valid.

Audio sample word length is carried in bits 33 through 35 of the Channel Status register over the HDMI link, as shown in Table 2.4 on the next page. These bits are always set to 0b101 when enabling the downsampler feature. Audio data is not affected because zeroes are placed into the LSBs of the data, and the wider word length is sent across the HDMI link.

<sup>© 2012-2017</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

|     |                   | Bit Comple Month conth |                                  |                    |      |

|-----|-------------------|------------------------|----------------------------------|--------------------|------|

| Aud | io Sample Word Le | ength                  | Maximum Word Length <sup>1</sup> | Sample Word Length | Note |

| 35  | 34                | 33                     | 32                               | (bits)             |      |

| 0   | 0                 | 0                      | 0                                | Not Indicated      | —    |

| 0   | 0                 | 1                      | 0                                | 16                 | 2    |

| 0   | 1                 | 0                      | 0                                | 18                 | 2    |

| 1   | 0                 | 0                      | 0                                | 19                 | 2    |

| 1   | 0                 | 1                      | 0                                | 20                 | 2, 4 |

| 1   | 1                 | 0                      | 0                                | 17                 | 2    |

| 0   | 0                 | 0                      | 1                                | Not Indicated      | 3    |

| 0   | 0                 | 1                      | 1                                | 20                 | 3    |

| 0   | 1                 | 0                      | 1                                | 22                 | 3    |

| 1   | 0                 | 0                      | 1                                | 23                 | 3    |

| 1   | 0                 | 1                      | 1                                | 24                 | 3, 4 |

| 1   | 1                 | 0                      | 1                                | 21                 | 3    |

#### Table 2.4. Channel Status Bits Used for Word Length

Notes:

1. Maximum audio sample word length (MAXLEN) is 20 bits if MAXLEN = 0 and 24 bits if MAXLEN = 1.

2. Maximum audio sample word length is 20.

3. Maximum audio sample word length is 24.

4. Bits [35:33] are always 0b101 when the downsampler is enabled.

#### 2.15.6. High-bitrate Audio on HDMI

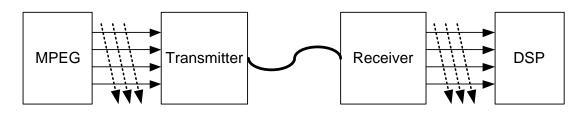

The high-bitrate compression standards, such as Dolby<sup>®</sup> TrueHD and DTS-HD Master Audio<sup>™</sup>, transmit data at bitrates as high as 18 Mb/s or 24 Mb/s. Because these bit rates are so high, Blu-ray decoders, HDMI transmitters (as source devices), and DSPs and HDMI receivers (as sink devices) must carry the data using four I<sup>2</sup>S lines rather than using a single very-high-speed S/PDIF interface or I<sup>2</sup>S bus (see Figure 2.7).

Figure 2.7. High-speed Data Transmission

The high-bitrate audio stream is originally encoded as a single stream. To send the stream over four I<sup>2</sup>S lines, the DVD decoder splits it into four streams. Figure 2.8 shows the high-bitrate stream before it has been split into four I<sup>2</sup>S lines, and Figure 2.9 on the next page shows the same audio stream after being split. Each sample requires 16 cycles of the I<sup>2</sup>S clock (SCK).

#### Figure 2.8. High-bitrate Stream before and after Reassembly and Splitting

Figure 2.9. High-bitrate Stream after Splitting

#### 2.15.7. I<sup>2</sup>S-to-SPDIF Conversion

The Sil9612 video processor includes audio processing to convert LPCM audio from the 2-channel I<sup>2</sup>S input or from the I<sup>2</sup>S output of the HDMI receiver to an IEC 60958 formatted audio stream. The converted audio stream is sent to the S/PDIF output pin. The conversion works only for 2-channel audio.

# 2.16.Audio Output Processing

The Sil9612 video processor supports audio extraction from the received HDMI/MHL streams. It can send the digital audio to a S/PDIF output, four I<sup>2</sup>S outputs (SD[3:0]), or six one-bit audio outputs. In addition, the audio output signals can be routed directly to the audio input ports of the HDMI transmitter using an internal audio data path.

Internal routing, multiplexing and processing of I<sup>2</sup>S and S/PDIF audio signals are illustrated in Figure 2.2 on page 9.

#### 2.16.1. S/PDIF Output

The S/PDIF output transmits 2-channel uncompressed LPCM data (IEC 60958) or a compressed bitstream for multichannel (IEC 61937) formats. The audio data output logic forms the audio data output stream from the HDMI audio packets. The S/PDIF output supports audio sampling rates from 32 kHz to 192 kHz. A separate master clock output (MCLK), coherent with the S/PDIF output, is provided for time stamping purposes.

#### 2.16.2. I<sup>2</sup>S Audio Output

An I<sup>2</sup>S output port with four data lines on the Sil9612 device enables 8-channel digital audio output at sample rates from 32 to 192 kHz. The I<sup>2</sup>S interface is highly programmable through registers to allow interfacing with a wide range of audio DACs or audio DSPs with I<sup>2</sup>S inputs. The I<sup>2</sup>S output port consists of signal pins AO\_MCLK, AO\_SCK, AO\_WS, and AO\_SD[3:0].

Additionally, an MCLK output signal is provided with a frequency that is programmable as an integer multiple of the audio sample rate  $f_s$ . MCLK frequencies support various audio sample rates as shown in Table 2.5.

| Multiple of f          | Audio Sample Rate, f <sub>s</sub> : I <sup>2</sup> S and S/PDIF Supported Rates |            |            |            |            |            |            |

|------------------------|---------------------------------------------------------------------------------|------------|------------|------------|------------|------------|------------|

| Multiple of <i>f</i> s | 32 kHz                                                                          | 44.1 kHz   | 48 kHz     | 88.2 kHz   | 96 kHz     | 176.4 kHz  | 192 kHz    |

| 128                    | 4.096 MHz                                                                       | 5.645 MHz  | 6.144 MHz  | 11.290 MHz | 12.288 MHz | 22.579 MHz | 24.576 MHz |

| 256                    | 8.192 MHz                                                                       | 11.290 MHz | 12.288 MHz | 22.579 MHz | 24.576 MHz | 45.158 MHz | 49.152 MHz |

| 384                    | 12.288 MHz                                                                      | 16.934 MHz | 18.432 MHz | 33.864 MHz | 36.864 MHz | —          | —          |

| 512                    | 16.384 MHz                                                                      | 22.579 MHz | 24.576 MHz | 45.158 MHz | 49.152 MHz | _          | _          |

#### **Table 2.5. Supported MCLK Frequencies**

The I<sup>2</sup>S output pins can be reconfigured as inputs for source-specific applications, such as a Blu-ray player where the SoC supplies the multichannel audio to the SiI9612 device directly through the I<sup>2</sup>S bus.

#### 2.16.3. One-bit Audio Output

The Sil9612 device can output six DSD/SACD streams and a clock for up to 6-channel support. The DSD streams are output on the multichannel I<sup>2</sup>S pins and the S/PDIF output pin according to Table 2.6. One-bit audio supports  $64 \cdot f_s$ , with  $f_s$  being 44.1 kHz or 88.2 kHz.

The one-bit audio outputs are synchronous to the positive edge of the DSD Clock. For one-bit audio, the sampling information is carried in the Audio InfoFrame instead of the Channel Status bits.

| Table 2.6. DSD | Output Pin      | iviapping |  |  |  |  |  |

|----------------|-----------------|-----------|--|--|--|--|--|

| DSD Signal     | Pin #           | Pin Name  |  |  |  |  |  |

| DCLK           | 33              | AO_SCK    |  |  |  |  |  |

| DRO            | 34              | AO_WS     |  |  |  |  |  |

| DL0            | 0 32 AO_SD0     |           |  |  |  |  |  |

| DR1            | 31              | AO_SD1    |  |  |  |  |  |

| DL1            | 30              | AO_SD2    |  |  |  |  |  |

| DR2            | 29              | AO_SD3    |  |  |  |  |  |

| DL2            | DL2 37 AO_SPDIF |           |  |  |  |  |  |

Table 2.6. DSD Output Pin Mapping

#### 2.16.4. High-bitrate Audio Support

The Sil9612 video processor supports the extraction of high-bitrate audio packets from the HDMI input. The extracted data is streamed out through the I<sup>2</sup>S output port on four I<sup>2</sup>S data lines at 192 kHz packet rate each.

Figure 2.10 shows the layout of the high-bitrate audio samples on the four I<sup>2</sup>S lines.

Figure 2.10. Layout of High-bitrate Audio Samples on I<sup>2</sup>S

#### 2.16.5. Auto Audio Configuration

The Sil9612 video processor can control the audio output based on the current states of CablePlug, FIFO, Video, ECC, ACR, PLL, InfoFrame and HDMI. Audio output is only enabled when all necessary conditions are met. If any critical condition is missing, the audio output is disabled automatically. Each of these events, which the logic monitors, can be turned on or off separately through a set of programmable registers.

#### 2.16.6. Soft Mute

On command from a register bit or when automatically triggered with Automatic Audio Control (AAC), the video processor progressively reduces the audio data amplitude to mute the sound in a controlled manner. This is useful when there is an interruption to the HDMI audio stream (or an error) to prevent any audio pop from being sent to the I<sup>2</sup>S or S/PDIF outputs.

# 2.17.CEC Interface

The Consumer Electronics Control (CEC) Interface block provides CEC electrically compliant signals between CEC devices and a CEC master. A CEC controller compatible with the Lattice Semiconductor CEC Programming Interface (CPI) is included on the chip. This CEC controller has a high-level register interface accessible through the I<sup>2</sup>C or SPI interface and can send and receive CEC commands. This controller makes CEC control very easy and straightforward, and removes the burden of having a host CPU perform these low-level transactions on the CEC bus.

# 2.18.GPIO

The Sil9612 video processor has four General Purpose I/O (GPIO) pins. Each GPIO pin supports the following functions:

- Input mode: The value can be read through a register.

- Output mode: The value can be set through a programmable register.

The GPIO pins can be reconfigured as a Serial Peripheral Interface (SPI) interface for programming the chip. Refer to the Pin Strapping section on page 25 for more information.

# 2.19.Control and Configuration

#### 2.19.1. Register/Configuration Logic

The register/configuration logic block incorporates all the registers required for configuring and managing the features of the Sil9612 video processor. These registers are used to perform HDCP authentication, audio/video/auxiliary format processing, CEA-861B InfoFrame packet format, and power-down control.

The registers are accessible from one of two I<sup>2</sup>C serial ports. The first is the DDC port located on the HDMI receiver port, and is connected through the HDMI cable to the upstream HDMI transmitter. It is used to exchange values between the transmitter and the SiI9612 video processor for HDCP operation. The second is the local I<sup>2</sup>C port that controls the SiI9612 device from the display system. The local device registers controlled by the display system can also be accessed through a Serial Peripheral Interface (SPI) bus.

The local device registers are accessed using a 16-bit addressing scheme. Refer to the Feature Information section on page 44 for details.

#### 2.19.2. I<sup>2</sup>C Serial Ports

The Sil9612 video processor provides three I<sup>2</sup>C serial interfaces:

- DDC receiver port to communicate back to the upstream HDMI or DVI host,

- DDC master port to read the EDID or perform HDCP authentication of the downstream device,

- I<sup>2</sup>C port for initialization and control by a local microcontroller in the display.

Refer to the Feature Information section on page 44 for a more detailed description of these serial ports.

The device address for the local I<sup>2</sup>C interface can be set as 0x30 or 0x32 through a strapping pin (see Table 2.7).

#### 2.19.3. SPI Serial Bus

The Sil9612 device SPI serial interface employs a simple four-wire synchronous serial interface with unidirectional data lines. The SPI interface allows the local microcontroller to access the Sil9612 device registers at up to 10 MHz bitrate. This is a more efficient method of configuring the device when compared to I<sup>2</sup>C mode.

Refer to the Feature Information section on page 44 for a more detailed description of SPI.

#### 2.19.4. Delay from Reset Deactivation to Register Access

Once the Reset pin of the Sil9612 device is deactivated, the software must wait 100 ns before accessing the device registers through either the local I<sup>2</sup>C or SPI bus.

# 2.20.Pin Strapping

The Sil9612 device supports pin strapping configuration to select the default device I<sup>2</sup>C address and the mode of the SPI pins. These settings are shown in Table 2.7. The logical value on these pins is latched by the Sil9612 device on the rising edge of RESET. See the

Digital Audio Output Pins table on page 40 for more information.

| Table | 2.7. | Pin | Strapping | Options |

|-------|------|-----|-----------|---------|

|-------|------|-----|-----------|---------|

| Pin Name          | Mode Name   | Description                                  |

|-------------------|-------------|----------------------------------------------|

| AO_MUTE           | I2C_ADDRSEL | Select I <sup>2</sup> C Address (0x30/0x32). |

|                   |             | 0 – Address 0x30                             |

|                   |             | 1 – Address 0x32                             |

| AO_SPDIF/DL2(OUT) | GPIO_MODE   | Select GPIO Mode.                            |

|                   |             | 0 – SPI pins used as SPI                     |

|                   |             | 1 – SPI pins used as GPIO                    |

# 2.21. Power Supply Sequencing

There are no power supply sequencing requirements for the Sil9612 device.

# 2.22. Audio PLL Reset

Once the Sil9612 device is powered on and all the power supplies of the device have reached their normal operating voltages, the audio PLL must be reset to ensure normal operation. The audio PLL is reset by asserting its Power Down bit for at least 1 ms.

# 3. Electrical Specifications

# 3.1. Absolute Maximum Conditions

#### Table 3.1. Absolute Maximum Conditions

| Symbol                   | Parameter                           | Min  | Тур | Max            | Units | Notes   |

|--------------------------|-------------------------------------|------|-----|----------------|-------|---------|

| IO_VDD33                 | I/O Pin Supply Voltage              | -0.3 |     | 4.0            | V     | 1, 2, 3 |

| IO_APVDD33               | Audio PLL I/O Supply Voltage        | -0.3 |     | 4.0            | V     | 1, 2, 3 |

| RX_AVDD10                | TMDS RX Analog 1.0 V Supply Voltage | -0.3 |     | 1.5            | V     | 1, 2    |

| RX_AVDD33                | TMDS RX Analog 3.3 V Supply Voltage | -0.3 |     | 4.0            | V     | 1, 2    |

| TX_AVDD10                | TMDS TX Analog Supply Voltage       | -0.3 | -   | 1.5            | V     | 1, 2    |

| TX_PVDD10                | TMDS TX PLL Supply Voltage          | -0.3 | -   | 1.5            | V     | 1, 2    |

| VP_AVDD10                | Video PLL Supply Voltage            | -0.3 | -   | 1.5            | V     | 1, 2    |

| AP_AVDD10                | Audio PLL Supply Voltage            | -0.3 | -   | 1.5            | V     | 1, 2    |

| DVDD10                   | Digital Logic Supply Voltage        | -0.3 | -   | 1.5            | V     | 1, 2    |

| IO_VDD5                  | I/O Pin 5 V Supply Voltage          | -0.3 | -   | 5.7            | V     | 1, 2    |

| VI                       | Input Voltage                       | -0.3 | -   | IO_VDD33 + 0.3 | V     | 1, 2    |

| V <sub>5V-Tolerant</sub> | Input Voltage on 5 V tolerant Pins  | -0.3 | -   | 5.7            | V     | —       |

| Tj                       | Junction Temperature                | _    | _   | 125            | °C    | _       |

| T <sub>STG</sub>         | Storage Temperature                 | -65  | _   | 150            | °C    | —       |

Notes:

1. Permanent device damage can occur if absolute maximum conditions are exceeded.

2. Functional operation should be restricted to the conditions described under normal operating conditions.

3. Voltage undershoot or overshoot cannot exceed absolute maximum conditions.

4. Refer to the Sil9612 Qualification Report for information on ESD performance.

# 3.2. Normal Operating Conditions

#### **Table 3.2. Normal Operating Conditions**

| Symbol         | Parameter                                | Min  | Тур | Max  | Units | Notes |

|----------------|------------------------------------------|------|-----|------|-------|-------|

| IO_VDD33       | I/O Pin Supply Voltage                   | 3.14 | 3.3 | 3.47 | V     | -     |

| IO_APVDD33     | Audio PLL I/O Supply Voltage             | 3.14 | 3.3 | 3.47 | V     | -     |

| RX_AVDD10      | TMDS RX Analog 1.0 V Supply Voltage      | 0.95 | 1.0 | 1.05 | V     | -     |

| RX_AVDD33      | TMDS RX Analog 3.3 V Supply Voltage      | 3.14 | 3.3 | 3.47 | V     | -     |

| TX_AVDD10      | TMDS TX Analog Supply Voltage            | 0.95 | 1.0 | 1.05 | V     | —     |

| TX_PVDD10      | TMDS TX PLL Supply Voltage               | 0.95 | 1.0 | 1.05 | V     | -     |

| VP_AVDD10      | Video PLL Supply Voltage                 | 0.95 | 1.0 | 1.05 | V     | —     |

| AP_AVDD10      | Audio PLL Supply Voltage                 | 0.95 | 1.0 | 1.05 | V     | -     |